製品

ランカスター大学の Michael Thompson 博士、 Jonathan Prance 教授、George Ridgard氏が、オックスフォード・インストゥルメンツのアプリケーションラボ (Apps Lab) に来社され、低温測定実験を行いました。弊社アプリケーション・サイエンティストであるAbi Graham博士が、その時の実験や様子について伺いました。

英国 Tubney にあるオックスフォード・インストゥルメンツ・ナノサイエンスの Apps Lab は、当社の製品や技術を開発することを目的として、昨年にオープンしました。ここでは、学術研究者や産業界の共同研究者と協力し、低温・高磁場環境の分野でより多くの研究をサポートすることが可能になります。また、ラボには12Tのマグネットを備えたTeslatron PTクライオスタットが設置されています。TeslatronPTは可変温度インサートを備えた無冷媒クライオスタットで、1.5〜300Kの温度を50mKの安定度で安定させることができます。クライオスタット本体に加え、レイクショアM81 Synchronous Source Measure SystemやレイクショアM91 Fast HallTM Measurement Controllerなど、電気輸送測定を行うための測定用電子機器も用意しています。

研究の方法と目的及び経緯について教えてください。

私たちの研究は、極低温で機能的な低電力エレクトロニクス、特に信号増幅器を必要とすることから始まりました。

主な目的は、低温(4K以下)で動作し、低電圧・低電力の回路にも使用できる金属-酸化膜-半導体電界効果トランジスタ(MOSFET)を見つけることでした。低電力と低電圧は、クライオスタットを加熱して温度安定性を損なったり、冷却装置を圧迫して試料測定を劣化させたりしないために不可欠な要素です。

極低温アンプは、S/N比を高め、サンプルの出力インピーダンスを下げることで、測定の帯域幅を広げます。この全体的な効果として、より小さな信号をより広い周波数範囲で測定することができ、極低温環境でより多くの物理量を測定することが出来ます。

今回テストした特定のMOSFETは、室温での超低消費電力回路用に設計されたものです。これにより、しきい値電圧、サブスレッショルド・スロープ、低温でのトランスコンダクタンスなど、回路設計に重要な特性を決定することができます。

最終的な目標は、低温で動作するMOSFETを見つけ、それを特性評価し、最終的にはアンプとして回路に使うことでした。

なぜ弊社アプリケーション・ラボを選択したのでしょうか?

主に、TeslatronPTを利用できることから、測定にはこちらのApps Labを選びました。このシステムの静的ヘリウムガス雰囲気は、電界効果トランジスタ(FET)を放熱するのに不可欠で、ランカスターにある真空雰囲気の無冷媒冷凍機では達成できなかったのです。

これは、FETの温度がチャネルの自己発熱によって取り付けられた放熱板の温度よりもはるかに高くなる可能性があるため、FETの低温測定では特に重要です。大電流はI-V特性を歪ませ、温度依存性測定の妨げとなってしまいます。

アプリケーションラボの測定にはどのような機器を用いましたか?

クライオスタットにはTeslatronPTを使用し、輸送測定には2台のKeithley2450 SMUを使用しました。デバイスは、放熱のためにセラミックの窒化アルミニウムPCBに16ピンDIPヘッダーで取り付けました。

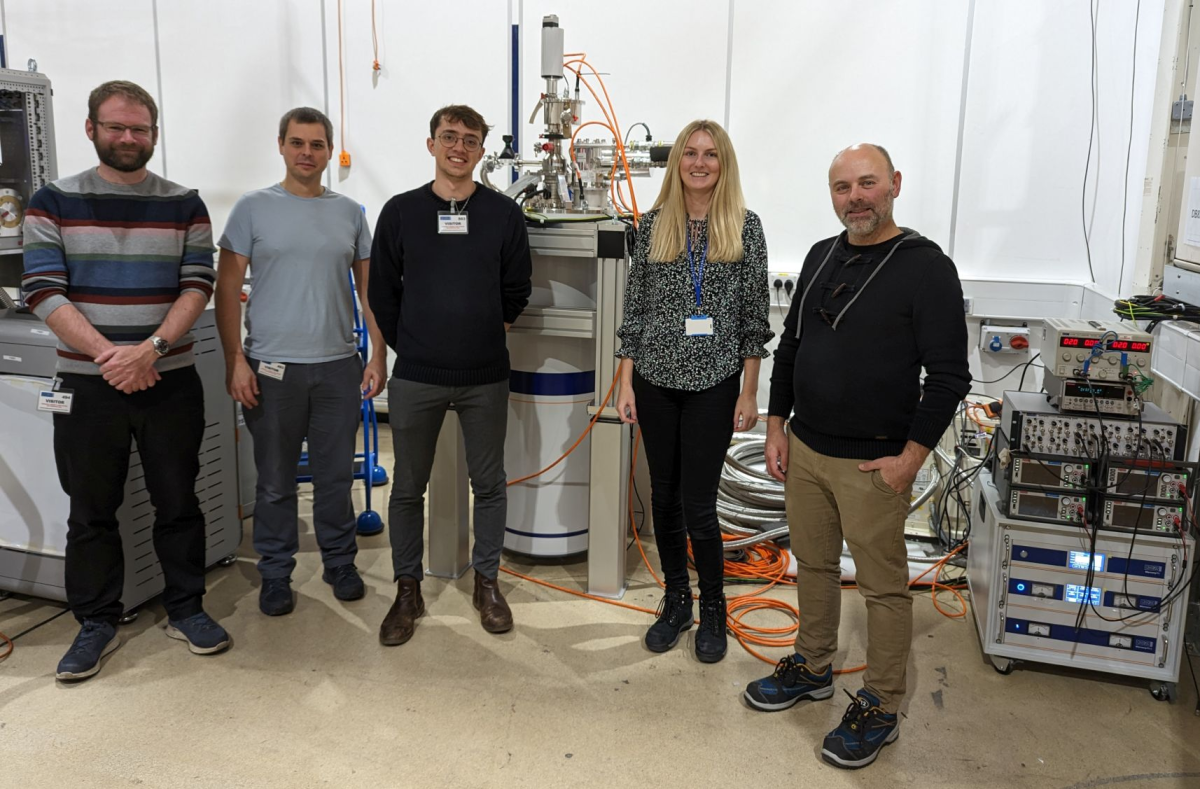

弊社アプリケーションラボを訪問したランカスター大学のチーム (左から Dr. Michael Thompson, Prof. Jonathan Prance,及びGeorge Ridgard) with と弊社のAbi Graham 及び Ben Yager

どのような結果が得られましたか?今後の研究にどのような影響が考えられますか?

すべてのFETが、サブスレッショルド・スロープの改善、飽和電流の増加、トランスコンダクタンスの増加、キンク効果など、よく理解されている低温変化を示しました。

その結果、3つのFETのうち2つのしきい値電圧が上昇し、低温での低電圧回路には適さないことがわかりました。3つ目の、低温でしきい値電圧がマイナスになるFETは、低温でのしきい値電圧が約0Vとなり、低電圧回路に適していました。

将来起こりうる影響としては、FETのドーピング/室温しきい値電圧を適切に考慮することで、より低消費電力で効率的な回路を構築できることが挙げられます。これは、量子コンピューティングなど、量子ビットのコヒーレント性を維持するために消費電力を最小化する必要があるアプリケーション用の回路を作成する極低温相補型金属酸化膜半導体(CMOS)設計者にとって興味深いことでしょう。

アプリケーションラボで実験した感想をお聞かせください。

非常に簡単で効率的でした。事前の連絡のおかげで、オックスフォード・インストゥルメンツ・ナノサイエンスのラボへ訪問する前にサンプルをマウントすることができましたし、到着してからはクライオスタット用のDIPマウントが利用できたため、実質的にボタンを押すだけでテストができました。

次はどのような研究をお考えでしょうか?

我々の研究がIEEE Journal Of the Electron Device Societyに掲載されることを期待しています。

また、低温でゼロに近いしきい値電圧を持つFETを作るために、CMOSを試運転する可能性もあります。ここでの目的は、より小さなノードを使用して、われわれがFETで発見したキンク効果のような影響を緩和し、低温、低ノイズ、低電力の多くのアプリケーションに対して、さらに適したものにすることです。

Abi Graham は弊社の測定科学者です。

George Ridgard はランカスター大学物理学専攻博士課程に在籍しています。